How to use the oscillator options on the UPduino?¶

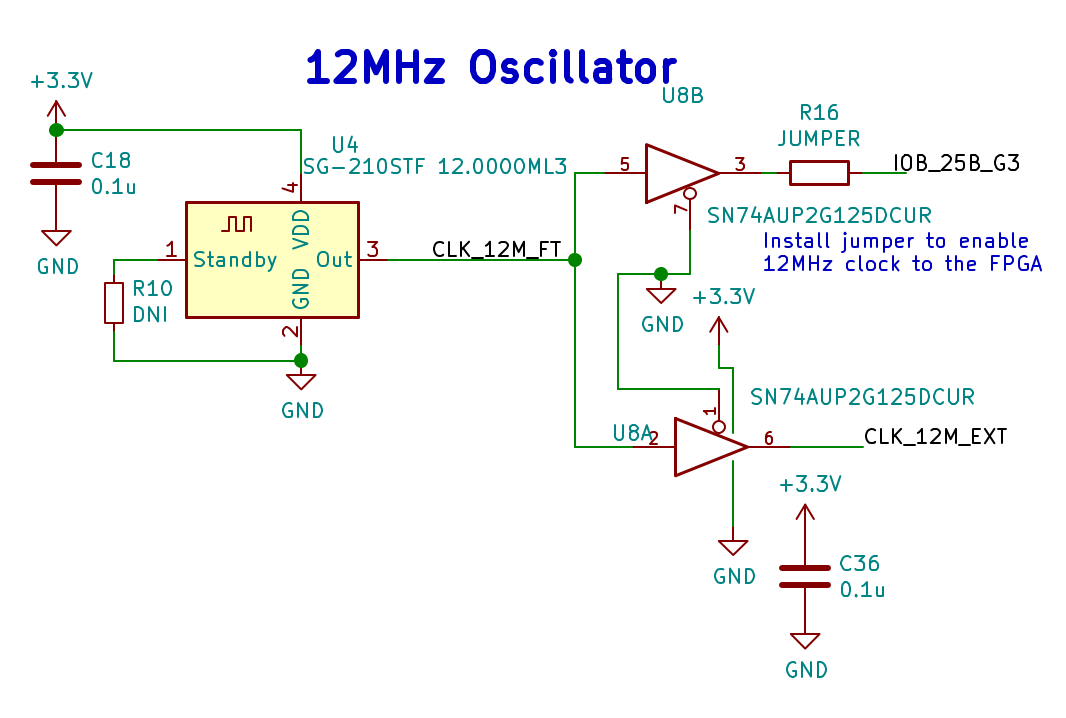

The UPduino has an on-board oscillator that generates 12MHz. This clock is generated by an oscillator and distributed to the FTDI, an external pin and also to a global buffer on the FPGA via an optional jumper.

The pin IOB_25B_G3 was chosen specifically as it is already in a bank thats forced to be at 3.3V levels. If any other global capable IO were to be used, this would force that IO bank to not be capable of the full flexibility of IO voltages.

The schematic portion is captured below:

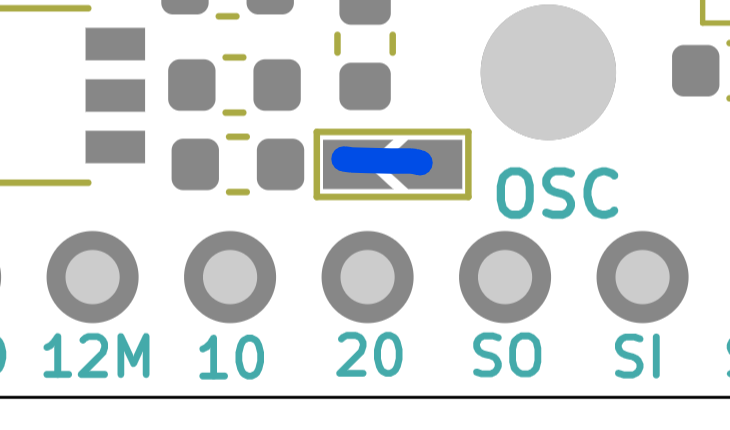

The 12MHz can be routed to the FPGA directly on the board to preserve signal quality and also to minimize external connection by shorting R16. Note that this marked as OSC on the silkscreen for clarity.